北京戴尔服务器代理商指出,这次芯片荒之所以引起热议,还因为并非单一种类的芯片缺货,而是消费电子、工业等各领域各类型芯片的全方面缺货。

在信息时代,芯片广泛用于各种电子产品和系统,是高*制造业的核心基石。虽然只有指甲盖大小,芯片却内有乾坤,能装下上千万甚至过亿的晶体管,代表着目前人类制造精密的工艺,因而其设计制造也具有很高的技术门槛。

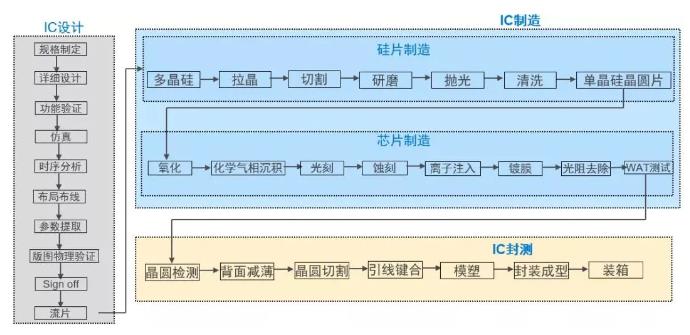

北京戴尔服务器代理商带您先来了解一下芯片“诞生记”。一般说来,芯片制造大致可分为三步,从上游的IC芯片设计,到中游的芯片制造,再到下游的封装测试。

芯片设计作为芯片产业链上游,是整个芯片制造流程中最难、也是具创新的重要环节,具有高投入、高风险特点。它分为前端设计(也称逻辑设计)和后端设计(也称物理设计):

前端设计

根据芯片规格书完成芯片的逻辑和集成,使用仿真验证工具完成SOC的设计验证。北京戴尔服务器代理商表示,该阶段有大量的小文件生成,对随机IOPS要求很高,并要求目录深度。

后端设计

根据前端设计产生的门级网表,通过EDA工具进行布局布线和物理验证。该阶段会生成很多大文件,对顺序IO性能和存储带宽有比较高的需求。

在设计阶段,工程师用硬件描述语言(HDL)完成设计文件,随后由计算机自动完成电路逻辑的编译、化简、优化、布局、布线和仿真,直至对特定目标芯片的适配编译和逻辑映射等工作。芯片的用途、规格、特性、制成工艺,全部是在这个阶段完成的规范和设计。

随着设计规模和复杂性不断增加,包含芯片设计在内的各种半导体设计工具需要在成千上万的高性能服务器上同时访问数百万个文件。由于芯片设计极其复杂,并且投入巨大,半导体公司非常重视该阶段的技术工艺及基础架构革新。

如同其它非结构化数据,半导体设计数据也在成倍地增长。每过渡到一个新的技术节点,对半导体行业的数据存储容量和性能要求都会增加一倍以上。而在这种指数级的数据增长和半导体设计需求变化中,半导体公司设计工作在存储架构方面面临着诸多瓶颈:

影响性能

传统的半导体设计存储架构需要在存储组件之间进行手动数据迁移,以平衡半导体设计应用的性能。以往都是限制每个控制器头的容量,以确保满足性能要求,但这会给控制器附加太多的容量使其处于饱和状态,这种情况随着容量增加而性能无法提高变得更糟。

磁盘空间利用效率低下

存储孤岛之间的容量利用不均衡导致一些存储卷没有得到充分利用,而另一些存储卷则被超额占用,其结果是有太多的存储卷需要管理。人工手动管理各个存储卷的数据和迁移数据以使其均匀分布,不仅破坏了性能,而且加重了运营负担。

多个管理点导致成本增加

传统的存储系统拥有多个管理点。每个存档者都需要单独管理,备份和复制也变得越来越复杂。这些都增加了总拥有成本和运营成本。缺乏集中管理还使半导体公司处于战略劣势,削弱了他们扩展存储的能力。

此外,考虑到大量的文件和目录,以及随着时间的推移,设计文件的规模越来越大,并需要进行验证测试,存储系统必须使文件管理变得简单,同时提供无缝、高性能的访问。

为了改变已经不适应目前半导体设计需求的传统存储架构,同时应对不断增加的吞吐量和IOPs需求,高性能存储解决方案成为解决问题的关键。